In occasione dell’IEEE International Electron Devices Meeting (IEDM) 2024, Intel Foundry ha fornito un’interessante anteprima sui progressi tecnologici ottenuti nel settore delle tecnologie dei transistor e di packaging che metterà in campo con i nodi produttivi futuri. L’obiettivo, comune a tutta l’industria dei semiconduttori, è quello di integrare fino a un trilione di transistor su un singolo chip, ma per far questo bisogna adeguare tutte le tecniche legate alla realizzazione di questi futuri progetti.

Si tratta di innovazioni importanti, nate e sviluppate per soddisfare le richieste sempre più esigenti legate soprattutto alla crescita esponenziale dell’Intelligenza Artificiale e a tutto il mercato che ci gira intorno. Ma non solo. L’azienda di Santa Clara ha un obiettivo molto importante, ovvero ripristinare definitivamente la propria leadership nella produzione di chip, in particolare negli Stati Uniti.

Come anticipato poco sopra, si tratta di tecnologie all’avanguardia che si diramano in diverse direzioni, con l’intento comune di far progredire l’azienda, ma più in generale il settore dei semiconduttori nell’arco del prossimo decennio. I progressi evidenziati da Intel riguardano diversi aspetti della realizzazione dei chip di prossima generazione, dai nuovi materiali che migliorano le interconnessioni interne del chip stesso, passando per tecniche avanzate di packaging che aiutano a migliorare produttività e rapidità di assemblaggio, arrivando alle tecnologie di realizzazione dei transistor. Ma vediamo insieme di cosa si tratta e cosa ha condiviso con la stampa il produttore statunitense.

Indice:

Intel Foundry e le nuove tecnologie che aiuteranno i nuovi nodi produttivi

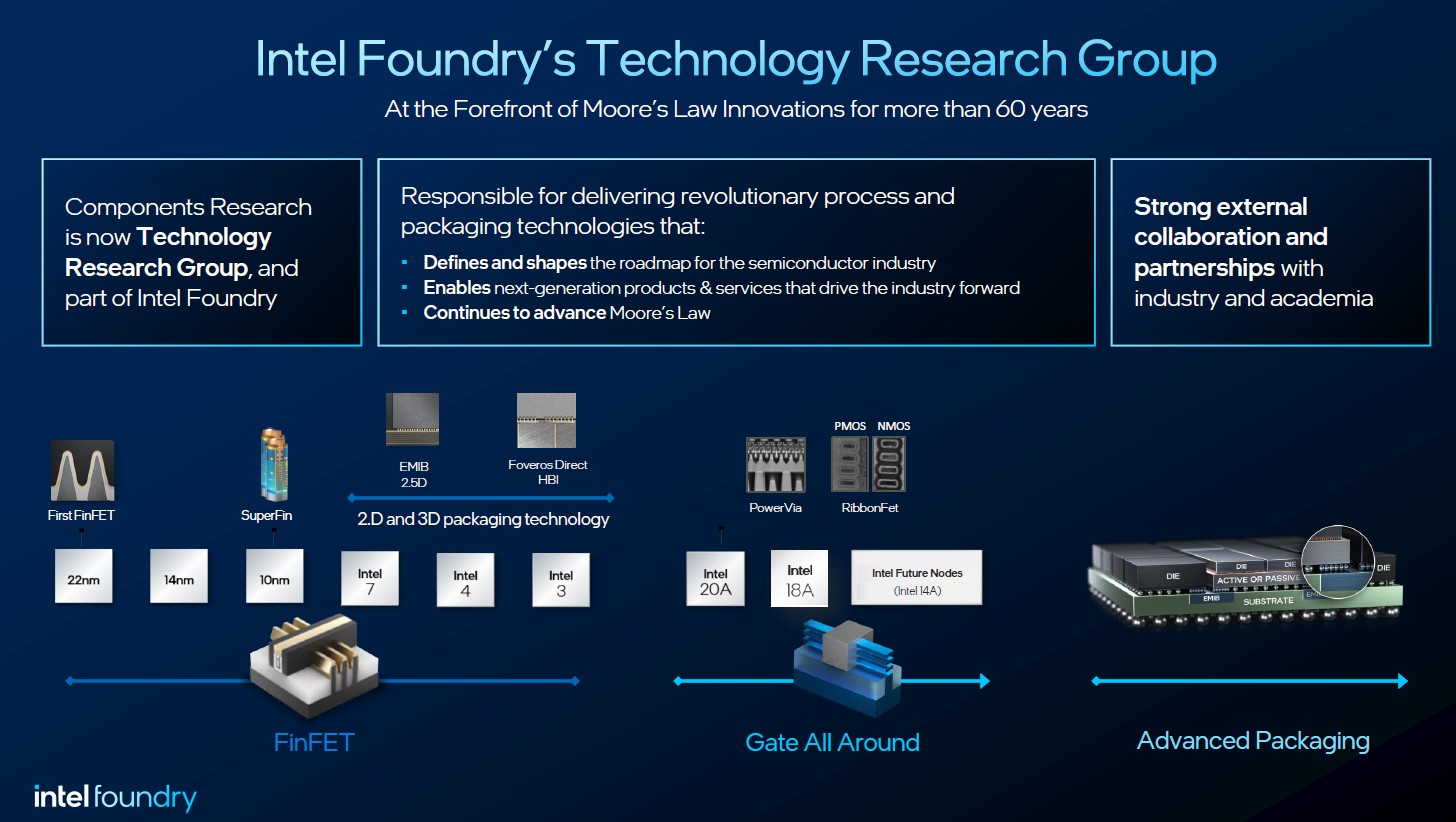

Anticipando che si tratta di argomenti che solitamente non vengono discussi nel segmento consumer, cerchiamo di capire in modo semplice quali sono i progressi fatti da Intel Foundry in questi ambiti. Prima però introduciamo il tutto con le parole di Sanjay Natarajan, Vicepresidente senior e Direttore generale, Intel Foundry Technology Research:

Intel Foundry continua ad aiutare a definire e modellare la tabella di marcia per il settore dei semiconduttori. Le nostre ultime innovazioni sottolineano l’impegno dell’azienda nel fornire tecnologia all’avanguardia sviluppata negli Stati Uniti, posizionandoci bene per aiutare a bilanciare la catena di fornitura globale e ripristinare la leadership tecnologica e manifatturiera nazionale con il supporto del CHIPS Act statunitense.

Tecnologie innovative per i transistor e il packaging dei chip di prossima generazione

Andando nelle specifico, Intel Foundry afferma di aver identificato diversi percorsi che risolvono le limitazioni previste dei transistor in rame per il ridimensionamento delle interconnessioni per i nodi futuri, migliorano le tecniche di assemblaggio esistenti e continuano a definire e modellare la roadmap dei transistor per il ridimensionamento gate-all-around. Tra i punti chiave per raggiungere tali obiettivi troviamo:

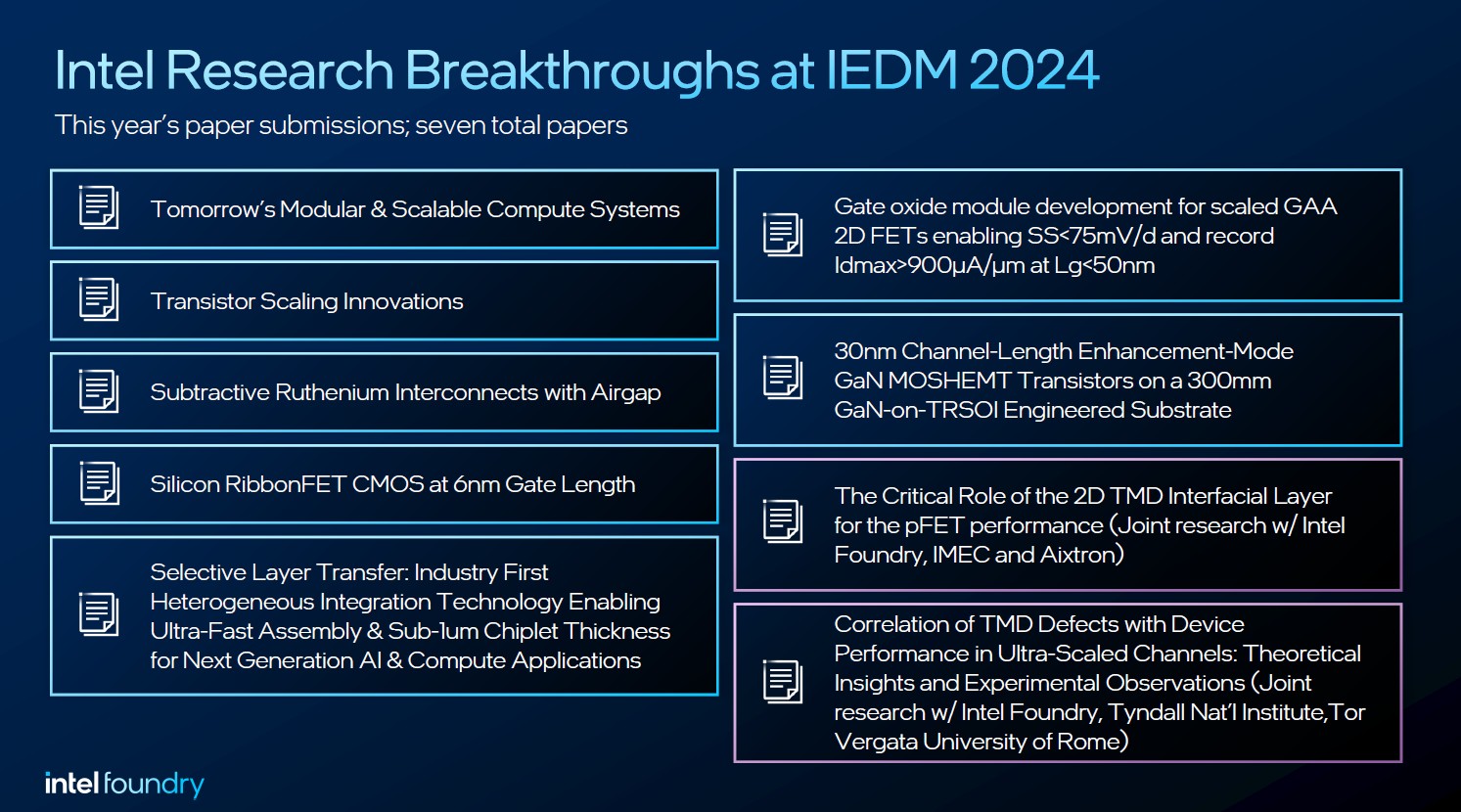

- Subtractive Ruthenium (Ru): per aiutare a migliorare le prestazioni e le interconnessioni all’interno dei chip, Intel ha introdotto il rutenio sottrattivo, un nuovo materiale di metallizzazione alternativo che utilizza la resistività a film sottile insieme agli airgap per fornire un significativo progresso nel ridimensionamento delle interconnessioni. L’implementazione di airgap con Ru sottrattivo ha fornito fino al 25% di riduzione della capacità da linea a linea a passi inferiori o uguali a 25 nanometri (nm), illustrando i vantaggi del Ru sottrattivo come schema di metallizzazione per sostituire il damasco di rame in strati di passo stretti.

- Selective Layer Transfer (SLT): il trasferimento selettivo di livello (SLT) è un’altra importante novità, in quanto permette di incrementare la produttività fino a 100 volte nell’assemblaggio chip-to-chip ultraveloce in packaging avanzato; si tratta di una soluzione di integrazione eterogenea che prevede chiplet ultrasottili con una flessibilità superiore che permette di ridurre sensibilmente le dimensioni del die, con rapporti di aspetto più elevati rispetto al tradizionale legame chip-to-wafer.

- Silicon RibbonFET CMOS: Intel Foundry ha presentato anche i transistor RibbonFET CMOS in silicio (semiconduttore a ossido di metallo complementare) con una lunghezza di gate di 6 nm ed effetti di canale corto, un approccio aggressivo che però dovrebbe aiutare sia in ottica prestazioni che dal punto di vista della scalabilità del silicio RibbonFET gate-all-around.

- Gate Oxide per FET 2D GAA scalati: per accelerare ulteriormente l’innovazione gate-all-around oltre il CFET, Intel Foundry ha presentato anche il suo lavoro sulla fabbricazione di transistor GAA 2D NMOS e PMOS con lunghezza di gate ridotta fino a 30 nm con un’attenzione specifica sullo sviluppo del modulo gate oxide (GOx).

La ricerca riporta le indagini del settore sui semiconduttori di dicalcogenide di metalli di transizione (TMD) bidimensionali (2D), che potrebbero sostituire in futuro il silicio nei processi avanzati dei transistor. Allo stesso tempo, Intel sta portando avanti la prima tecnologia al nitruro di gallio (GaN) da 300 millimetri del settore, una tecnologia emergente per l’elettronica di potenza e radiofrequenza (RF) in grado di offrire prestazioni più elevate e sostenere tensioni e temperature più elevate rispetto al silicio.

In quest’ottica Intel parla anche di MOSHEMT GaN (transistor ad alta mobilità di elettroni), realizzati su un substrato GaN-on-TRSOI (“trap-rich” silicon-on-insulator) da 300 mm. I substrati di progettazione avanzata come GaN-on-TRSOI possono ottenere prestazioni migliori nelle applicazioni RF, oltre che nell’elettronica di potenza, il tutto riducendo la perdita di segnale e ottenendo una migliore linearità del segnale con schemi di integrazione avanzati che possono essere realizzati tramite l’elaborazione del substrato sul retro.

In chiusura, Intel Foundry ha anche esposto la sua visione per il futuro del packaging avanzato e della scalabilità dei transistor per soddisfare le richieste in tutte le applicazioni, inclusa l’Intelligenza Artificiale. Il produttore ha identificato tre punti chiave per l’innovazione in ottica AI, sempre riservando un posto primario all’efficienza energetica; nel dettaglio:

- Integrazione avanzata della memoria per eliminare i colli di bottiglia per capacità, larghezza di banda e latenza

- Legame ibrido per l’ottimizzazione della larghezza di banda di interconnessione

- Espansione del sistema modulare con nuove soluzioni di connettività corrispondenti

Molta carne al fuoco quindi per Intel Foundry che punta a riportare la leadership dei semiconduttori a Santa Clara, non solo per performance, ma anche per modularità, scalabilità ed efficienza; chiudendo proprio in tema efficienza, Intel Foundry ha evidenziato come lo sviluppo di un transistor in grado di funzionare a bassissima tensione (meno di 300 millivolt) aiuterà ad affrontare i crescenti colli di bottiglia termici e si tradurrà in notevoli miglioramenti nel consumo energetico e nella dissipazione termica.

I nostri contenuti da non perdere:

- 🔝 Importante: Queste cuffie CMF by Nothing a meno di 25 euro su Amazon sono imperdibili

- 💰 Risparmia sulla tecnologia: segui Prezzi.Tech su Telegram, il miglior canale di offerte

- 🏡 Seguici anche sul canale Telegram Offerte.Casa per sconti su prodotti di largo consumo